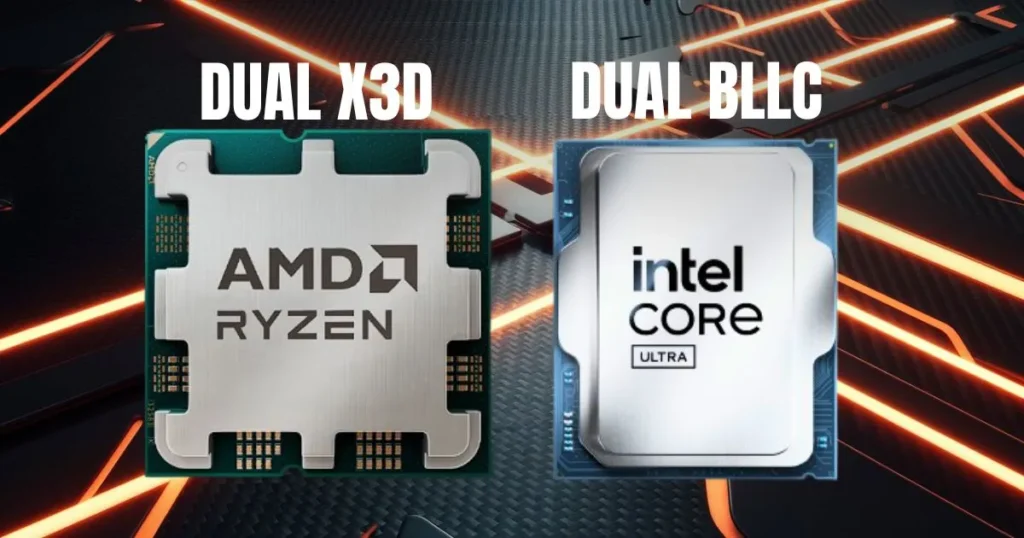

The Next Frontier: AMD and Intel Race Toward Dual 3D Cache Designs

In a stunning coincidence, leaks about dual stacked cache designs from both AMD and Intel surfaced simultaneously, signaling a major shift in CPU architecture. According to industry insiders, both companies are developing processors with two high-capacity cache layers – a move that could push total cache beyond 200MB for unprecedented AI and gaming performance.

The Leaks Explained

- Intel’s Dual-BLLC (Big Last Level Cache):

- Intel’s updated roadmap reportedly includes SKUs with two BLLC units (Intel’s 3D V-Cache equivalent).

- Preliminary specs suggest 200MB+ total cache – a massive jump from current 140MB rumors.

- Targets next-gen Nova Lake architecture (late 2026).

- AMD’s Dual-X3D:

- Leaked plans indicate dual stacked cache chiplets on Zen 5-based CPUs.

- Builds on existing Zen 5-X3D technology but doubles cache capacity.

- Could launch years before Intel’s solution (2024-2025).

Why Dual Cache Matters

- AI/LLM Revolution: Large language models thrive on massive cache for faster data access.

- Gaming Performance: Current 3D V-Cache chips already dominate gaming benchmarks.

- Competitive Pressure: AMD may have leaked plans intentionally to counter Intel’s roadmap.

Simplified comparison of cache configurations (conceptual)

Technical Challenges

AMD’s Project Hydra team reportedly flagged key hurdles:

Cache Asymmetry: Balancing performance across heterogeneous cache layers is complex.

Thermal Constraints: Stacked cache increases heat density.

Cost vs. Benefit: Yield challenges must justify performance gains.

I can't confirm this, but AMD is really worried about performance degradation due to heterogeneous cache asymmetry since Microsoft can't do anything about it.

— 1usmus 🇺🇦 (@1usmus) August 4, 2025

Industry Context

- AMD’s Current Lead: Existing 3D V-Cache chips (e.g., Ryzen 7 5800X3D) already outperform Intel in cache-sensitive tasks.

- Intel’s Catch-Up: BLLC is critical to closing the gaming/AI performance gap.

- Market Timing: AMD could launch dual-X3D in 2025 while Intel targets late 2026.

Important Caveats

- Early-Stage Rumors: No official confirmation from AMD/Intel.

- Roadmaps Change: Specs and timelines may shift (especially Intel’s 200MB claim).

- Leak Source: Panzierlied (Chiphell) has credible track record with GPU leaks.

Also, Read

- AMD AM6 Socket Leak – 2100+ Pins, PCIe 6, DDR6 – and AM5 Cooler Compatibility?

- AMD Radeon RX 9060 Leak – 18Gbps GDDR6, Lower Clocks & OEM-Exclusive Focus

- AMD Ryzen 9000 Leak Reveals 16-Core Zen5 Beast – 192MB Cache, 200W TDP

The Bottom Line

The simultaneous leaks suggest an industry-wide pivot toward cache-centric designs. If realized, dual-stacked cache could redefine high-performance computing – making 200MB+ caches the new battlefield for AI, gaming, and productivity dominance.

Source: chiphell, bitsandchips